引言

在AI集群和超大规模数据中心进入高速迭代周期的今天,带宽需求与能效瓶颈的矛盾已成为网络架构演进的核心驱动力。GPU等高性能计算核心功耗持续攀升,推动互连功耗在系统能耗结构中的占比快速上升;而传统电互连在信号完整性、传输距离和热设计上的物理极限,正加速倒逼光电融合技术的落地。硅光子技术凭借与CMOS工艺的高度兼容性与优异的集成能力,成为下一代高速互连的关键平台,其中,线性驱动可插拔(LPO)与共封装光学(CPO)代表了两条不同的技术演进路径。LPO延续了可插拔架构的成熟生态与低部署风险,在中速率场景中具备显著竞争力;而CPO通过将光引擎直接与ASIC共封装,在超高速与高密度架构中展现出更高的能效与扩展潜力。随着200G/通道及224G+速率时代的临近,LPO与CPO的竞争与互补关系,将在未来五年内深刻影响数据中心网络的技术格局与产业链生态。

以下是对报告内容的梳理总结——————————————

一、技术背景与发展动因

1. 数据中心与AI集群的带宽与功耗瓶颈

AI训练与推理的算力需求正推动GPU等高性能芯片功耗快速攀升,单机架功耗已由125kW提升至600kW,并可能在短期内突破1MW。过去功耗优化集中在计算核心,但随着I/O速率持续提升以匹配计算能力,高速电互连的功耗占比迅速上升。在100Gbps及以上速率下,SerDes与均衡电路功耗已接近甚至超过交换芯片核心逻辑。10G模块功耗仅约1W,而800G与1.6T模块分别达到15W与30W,在高端交换机中,光模块功耗可占系统总功耗的40%以上,令互连环节成为能效优化的关键瓶颈。

2. 电互连物理极限与信号完整性挑战

在多百Gbps速率下,铜迹线与铜缆传输接近物理极限。趋肤效应、介质损耗和阻抗不连续导致反射与失真,PAM4虽在相同符号速率下实现数据速率翻倍,但信号裕量缩小、抗干扰能力下降,需更高Eb/No以维持误码率。在200Gbps/通道下,被动铜缆(DAC)传输不足1米,主动铜缆(ACC)也仅约3米,难以满足跨机架需求。引入DSP、FEC、低损耗PCB材料虽可改善信号质量,但增加延迟、功耗与成本。

3. 硅光子技术的集成优势与平台特性

硅光子(SiP)在硅基片上集成光子器件与CMOS电路,将电-光转换路径从厘米级缩短至毫米级,显著优化功耗与延迟。其优势包括:缩短电连接降低SerDes能耗、释放面板空间提升带宽密度,以及与InP、GaAs激光器及TFLN、BTO等新型调制材料的兼容性。硅光子已成为LPO与CPO的核心技术基础,并有望成为未来高速光互连的统一集成平台。

4. LPO与CPO技术概述及发展路径

LPO(Linear Pluggable Optics)通过取消光模块内DSP,依赖主机ASIC SerDes完成信号均衡与恢复,功耗显著降低(800G LPO仅2–4W),并保留可插拔的模块化与多供应商生态。但在200G/通道速率下的可行性尚无公开验证。

CPO(Co-Packaged Optics)将光引擎与ASIC共封装,将电连接缩短至毫米级,实现更低功耗(可低至1pJ/bit)、更低延迟与更高面板密度。其路径包括遵循标准的CPO方案以及深度定制的协同优化CPO。未来1.6T、3.2T等超高速场景下,CPO被认为更具可行性,中短期内两者将并行发展。

二、CPO的价值主张与技术实现

1. CPO缩短电连接路径的核心优势

CPO(Co-Packaged Optics)的根本价值在于消除主机ASIC与光收发器之间的长距离高速电通道,将光引擎直接集成于与ASIC同一封装基板,使电连接路径从数厘米缩短至毫米级。这种架构显著减少信号衰减与失真,使SerDes能够在低功耗模式下运行,并降低延迟与成本。采用OIF标准化的XSR等短距接口,可在无需高功耗DSP或重定时器的前提下节省30–50%的功耗,部分早期系统已实现低于1pJ/bit的能效水平。

2. 低功耗、低延迟与高带宽密度的实现机制

CPO通过极短的电路径降低了SerDes能耗,减少了均衡与FEC处理需求,从而削减数十纳秒延迟,对AI/HPC等延迟敏感型应用尤为有利。光引擎的封装集成释放了前面板空间,替代体积较大的QSFP-DD/OSFP模块,配合MPO或VSFF等高密度连接器,OIF 3.2T CPO设计可实现约140 Gbps/mm的“海滩线密度”,显著提升系统端口密度。

3. 标准化方案与协同优化方案对比(2D、2.5D、3D封装)

- 标准化CPO:遵循IEEE 802.3等既有光接口标准(如SR4、DR4、FR4),多采用2.5D集成,将光芯片置于ASIC外围互连基板上,确保与现有光模块生态互通,功耗优化主要源于取消DSP。

- 协同优化CPO:通过定制电光接口与封装架构(如3D封装、TSV、混合键合等),将光芯片近贴或堆叠于ASIC核心区,实现极短并行电连接,进一步突破功耗与带宽密度瓶颈。但该模式牺牲标准接口互通性,对ASIC设计、热管理与制造良率要求更高。

4. 电接口演进:XSR、VSR、UCIe等标准

CPO普遍采用XSR(Extra Short Reach)、VSR(Very Short Reach)等短距SerDes接口,以112Gbps PAM4为例,XSR模式的功耗远低于中长距(MR/LR)模式,且在ASIC总功耗中占比更小。随着UCIe等芯粒互连标准的发展,结合25–55 μm凸点间距的先进封装,可实现<0.5 pJ/bit的能效,未来3D封装目标甚至低于0.05 pJ/bit。

5. 可靠性与热管理挑战及外部激光源(ELS)架构

CPO将光器件置于高功率ASIC邻近位置,带来显著的热与寿命风险。外部激光源(ELS)架构通过将高功率CW激光器移至机箱前面板或独立模块,将光通过光纤引入CPO引擎,从而改善热稳定性并便于独立更换故障器件。这一方案提高了激光器可靠性与维护性,但也引入光纤布线复杂度、光功率预算损耗及连接器长期可靠性等新挑战。

三、LPO与CPO的性能与应用比较

1. LPO在功耗、可维护性和生态成熟度上的优势

LPO(Linear Pluggable Optics)通过取消光模块内的DSP/重定时器,显著降低功耗。以800G模块为例,LPO功耗通常为2–4W,相较于DSP型可插拔模块(10–14W)可减少约35%的系统级能耗。其保留了可插拔架构的全部运营优势,包括模块化、热插拔、独立生命周期管理以及多供应商采购能力,依托成熟标准与生态,部署风险低、兼容性高,适合大规模数据中心的快速部署与迭代。

2. CPO在带宽密度与未来速率演进(200G/224G+)的潜力

CPO(Co-Packaged Optics)通过将光引擎与ASIC共封装,实现极短电路径与优化接口设计,在信号完整性、延迟控制及带宽密度方面优势显著。特别是在200G/通道、224G+/通道及更高端口密度系统中,CPO能够突破LPO的物理尺寸与信号传输瓶颈。其封装边缘与系统面板的带宽密度高于LPO,适用于面板面积受限的超高性能交换机和AI/HPC集群。

3. 系统功耗对比与全生命周期运营考量

LPO在现有800G系统中具备较高的功耗优势,但在1.6T及更高端口速率下,功耗差距缩小。CPO的额外节能主要来自缩短电连接路径和减少DSP需求,典型1.6T端口功耗约8–10W(Ranovus案例约5 pJ/bit,即8W),低于同类LPO设计的约10W和LRO的18W。但CPO将光引擎与ASIC绑定,系统故障时需更换整机或整板,增加了MTTR与维护成本,对运维团队的技能与备件管理提出更高要求。

4. LPO、CPO在不同速率与场景下的适用性分析

- LPO:在100G/通道与800G系统中具备优异的性价比和生态适配性,适合对能效、成本和可维护性要求均衡的场景,如大型互联网数据中心和云服务商现网升级。

- CPO:在200G/通道、1.6T/3.2T及更高密度的高端交换机、AI/HPC集群中优势明显,适合面向超高速、低延迟和高带宽密度的前瞻部署。随着ASIC SerDes从100G过渡到200G及以上,CPO的功耗与性能优势将进一步放大,成为未来高性能网络的主流形态。

四、产业生态与关键厂商布局

1. 产业链结构与核心参与者角色

CPO(Co-Packaged Optics)产业链覆盖芯片设计—光子器件—封装制造—系统集成—最终用户五大环节,涉及多类核心主体:

- 芯片与ASIC厂商:Broadcom、Cisco、Intel、NVIDIA、Marvell、AMD等,负责高性能交换芯片与GPU/XPU设计,主导SerDes架构及CPO集成策略,部分通过收购或合作引入光子技术。

- 系统设备商:Cisco、Arista Networks、Juniper Networks等,将CPO/光学接口嵌入交换机、路由器、服务器等整机方案中。

- 光子器件与模块厂商:涵盖硅光子与PIC设计(Intel、Ayar Labs、Ranovus、Nubis Communications、Lightmatter、Celestial AI、Sicoya、Scintil Photonics、POET Technologies)、激光器及ELS供应商(Lumentum、Casela、Nexus Photonics、Coherent、Furukawa、Sumitomo Electric、Quintessent、Sivers Photonics)、连接器与光缆厂商(Molex、TE Connectivity、SENKO、US Conec)。

- 制造与封测服务商:TSMC、GlobalFoundries、STMicroelectronics、AIM、SPIL、ASE、ficonTEC、Amkor,提供先进封装、光电混合集成及批量测试能力。

- 标准组织与产业联盟:OIF、IEEE 802.3、各类MSA(如CW-WDM MSA)推动接口、组件及系统层面标准化。

- 最终用户:Meta、Google、Microsoft、AWS、Alibaba、Tencent、Oracle、IBM等超大规模云厂商与运营商,是需求驱动与生态塑造的核心力量。

2. 头部芯片厂商策略

- Broadcom:OFC 2023展示Tomahawk5 CPO版本“Bailly”,集成6.4T第二代光引擎,功耗较DSP模块降低50%。Micas Networks已推出基于Bailly的51.2T CPO交换机(128×400G-FR4,4U),采用前面板插拔ELS。计划2026年发布Tomahawk6(TH6)CPO版本“Davisson”,支持200G DR4接口、全液冷设计,目标8W/1.6T端口功耗。

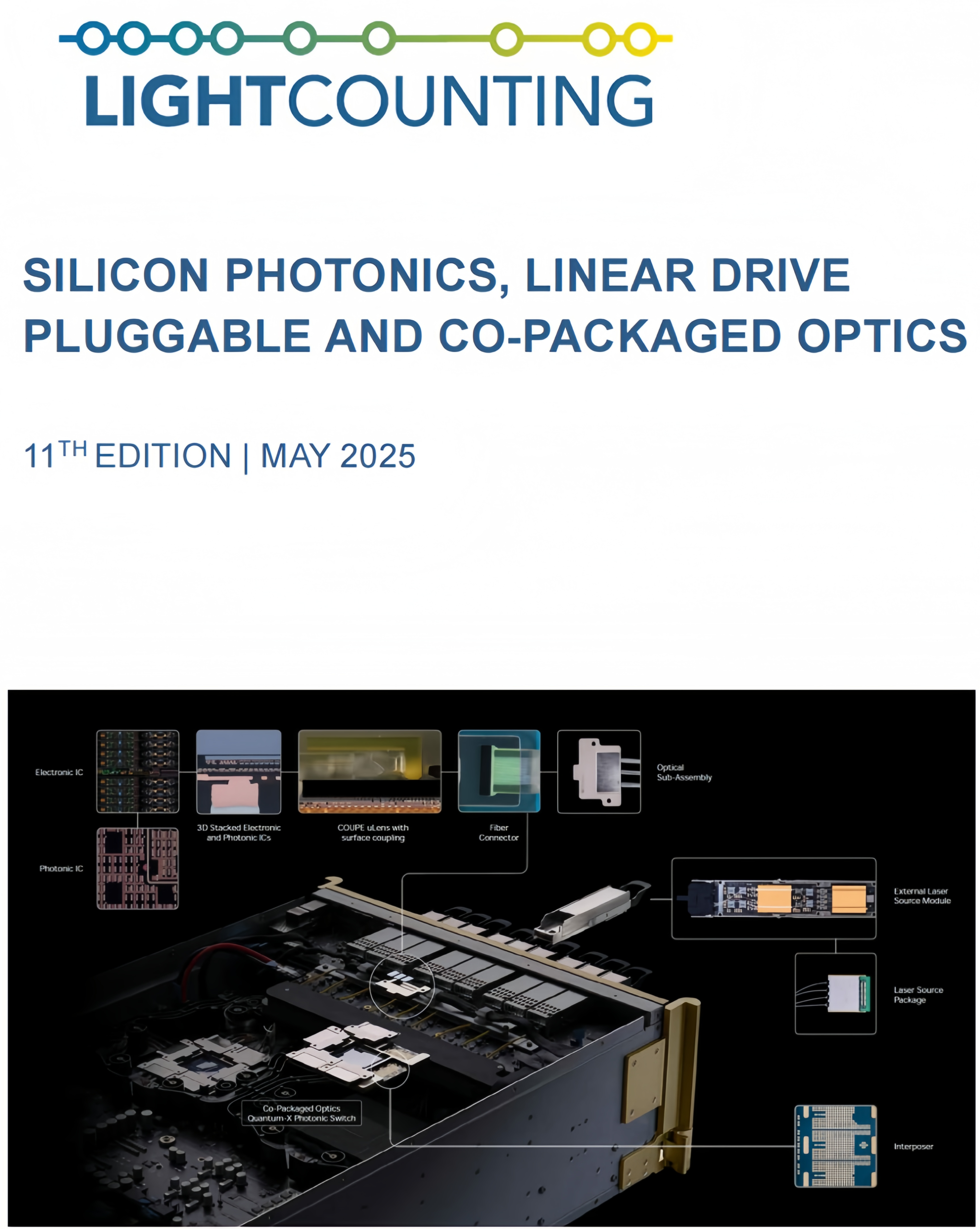

- NVIDIA:GTC 2025发布CPO交换机系列,涵盖InfiniBand(Quantum-X Photonics)与Ethernet(Spectrum-X Photonics),分别于2025下半年与2026下半年上市。采用微环调制器(MRM)实现9W/1.6T端口功耗(含7W光引擎+2W ELS),与TSMC合作完成电子与光子3D堆叠(COUPE技术),SPIL负责封测,光器件供应商包括Lumentum、Sumitomo Electric、Coherent。

- AMD、Intel、Marvell:通过收购或合作布局CPO与光I/O技术,强化在AI/HPC与高性能网络中的竞争力。

3. 光子芯片与模块企业技术亮点

- Ranovus:ODIN系列CPO方案,集成量子点多波长激光阵列与硅光子技术,支持800G–3.2T,功耗<5pJ/bit;与Cerebras获美军4500万美元合同开发新一代光互连。

- Lightmatter:3D CPO(L200/L200X),通过Passage光互连基板将电IC直接堆叠,支持32–64Tb/s封装带宽,多ASIC封装可达114Tbps(M1000平台)。

- Celestial AI:采用GeSi EAM调制器,具备宽光谱(>30nm)、高温稳定性(温漂0.77nm/°C),可在ASIC高热环境下运行,支持内存池化与计算-内存分离架构。

- Ayar Labs:TeraPHY CPO引擎,8Tbps双向带宽,基于UCIe接口,外部SuperNova光源可同时支持1Pbps互连。

- Nubis Communications:2D多行高密度光I/O,I/O密度达246Gbps/mm(单芯片),可扩展至985Gbps/mm(四行封装),功耗3.9pJ/bit。

- Avicena:基于GaN微LED阵列的多并行通道架构,单通道<1pJ/bit,总带宽>1Tbps/mm,适用于≤10m短距互连。

4. 制造与封装服务商能力与合作模式

- TSMC:为Broadcom、NVIDIA、Ayar Labs等提供先进2.5D/3D封装与光电集成工艺。

- GlobalFoundries、STMicroelectronics:提供硅光子平台及混合集成代工能力。

- SPIL、ASE、Amkor:在光电异质集成、精密对准、批量封测领域具备成熟能力,并与头部芯片厂深度绑定。

5. 标准组织与产业联盟的推进作用

OIF、IEEE 802.3及多类MSA组织在接口、组件和系统层面推动标准化,旨在降低多厂商互通壁垒,促进CPO规模化商用。但目前系统级互操作标准仍滞后,CPO的多供应商生态建设尚处早期阶段。

五、市场规模与发展预测(2025–2030)

1. 按技术路线划分的市场预测(SiP、InP、GaAs、TFLN等)

未来五年,光互连市场将沿多技术路线并行演进:

- SiP(硅光子):依托CMOS工艺成熟度与与电子电路高集成度的优势,将在数据中心、AI集群和高性能计算(HPC)中占据主导,预计2025–2030年复合增长率(CAGR)超过20%。

- InP(磷化铟):在长距传输与DWDM系统中维持高功率与低损耗优势,适用于城域网与骨干网应用,市场保持稳定增长。

- GaAs(砷化镓):在特定高速光电子器件(如VCSEL)中具备竞争力,主要用于短距互连与消费级高速光链路。

- TFLN(薄膜铌酸锂)、BTO(钛酸钡)及聚合物材料:作为新一代高带宽、低驱动电压调制器材料,将逐步与SiP平台集成,推动400G/800G以上系统功耗下降与速率提升。

2. 按应用场景细分的需求趋势(以太网、DWDM、AI集群等)

- 以太网(Ethernet):超大规模数据中心升级驱动800G/1.6T端口需求,CPO和LPO方案将同时渗透,但1.6T以上速率CPO占比快速提升。

- DWDM:受益于骨干网扩容及城域网升级,InP平台持续占优,高速相干光模块需求稳步增长。

- AI集群与HPC:AI训练与推理集群带宽需求呈指数级增长,224G/通道及更高速率端口将在2027–2030年成为主流,CPO渗透率显著提高。

- 存储网络与内存互连:新型内存池化与计算-存储分离架构加速光互连在机架内、机架间的应用落地。

3. LPO/CPO渗透率与出货量预测

- LPO(Linear Pluggable Optics):短期(2025–2027年)在800G与部分1.6T端口中保持主流,占据超过60%的出货份额,依托成熟生态与可插拔特性满足主流数据中心升级。

- CPO(Co-Packaged Optics):中期(2027–2030年)在1.6T及3.2T超高速场景中快速提升份额,预计到2030年在超大规模AI/HPC集群中渗透率可超过50%,并逐步取代LPO在顶级性能段的地位。

- 整体出货量:全球高速光模块与光引擎出货量将在2025–2030年保持双位数增长,CPO驱动的封装级光引擎市场规模将实现数倍扩张。

4. 光子芯片市场价值增长的驱动因素

- 带宽需求爆发:AI集群、云计算与边缘计算对端到端低延迟、高吞吐互连的刚性需求,推动高速光I/O需求持续扩张。

- 功耗优化压力:数据中心功耗上限提升有限,促使CPO等低功耗光互连技术加速替代高功耗电互连方案。

- 封装与材料创新:2.5D/3D异质集成、先进调制器材料(TFLN、BTO、聚合物)与外部激光源架构显著提升系统性能与集成度。

- 标准化与生态建设:OIF、IEEE及各类MSA推进接口与组件标准,降低多厂商互通壁垒,促进CPO规模化商用。