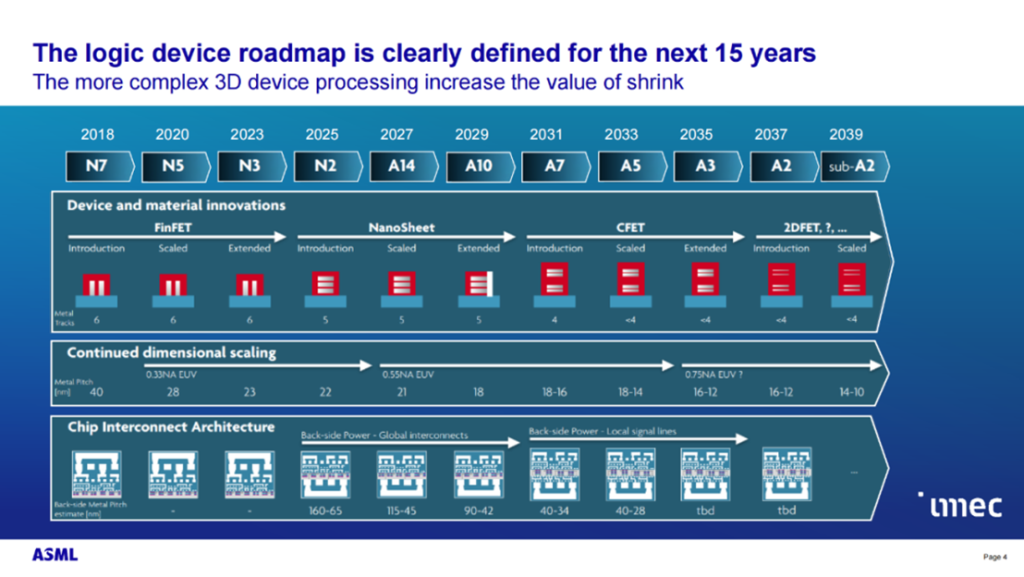

1. 技术背景与发展脉络

- 摩尔定律延续需求:逻辑器件路线图未来 15 年清晰,3D 工艺复杂度增加,更需要更高分辨率的光刻。

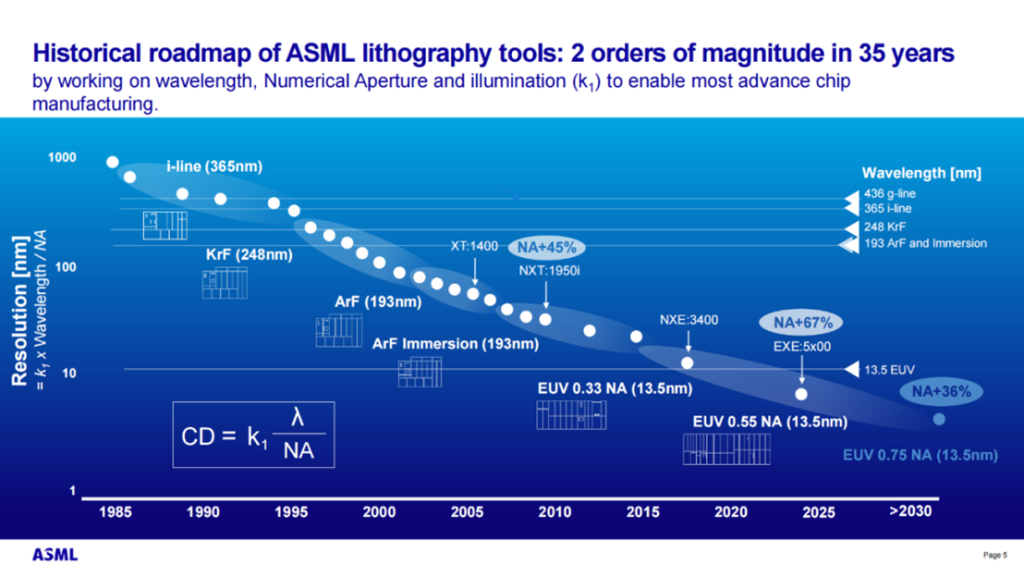

- ASML 光刻技术演进:35 年内通过波长缩短(i-line→KrF→ArF→EUV)、数值孔径(NA)提升和照明优化,实现两数量级分辨率提升。

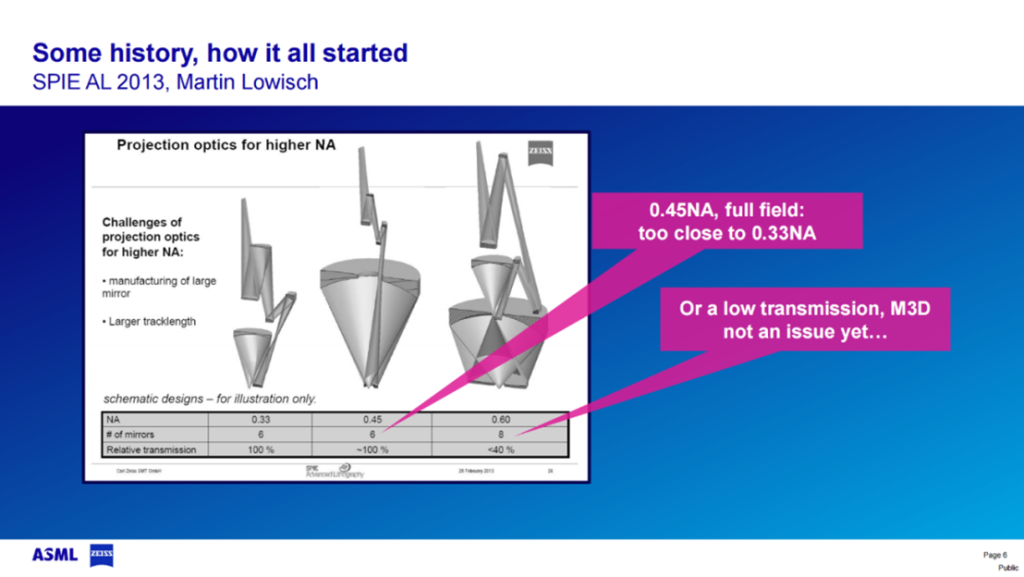

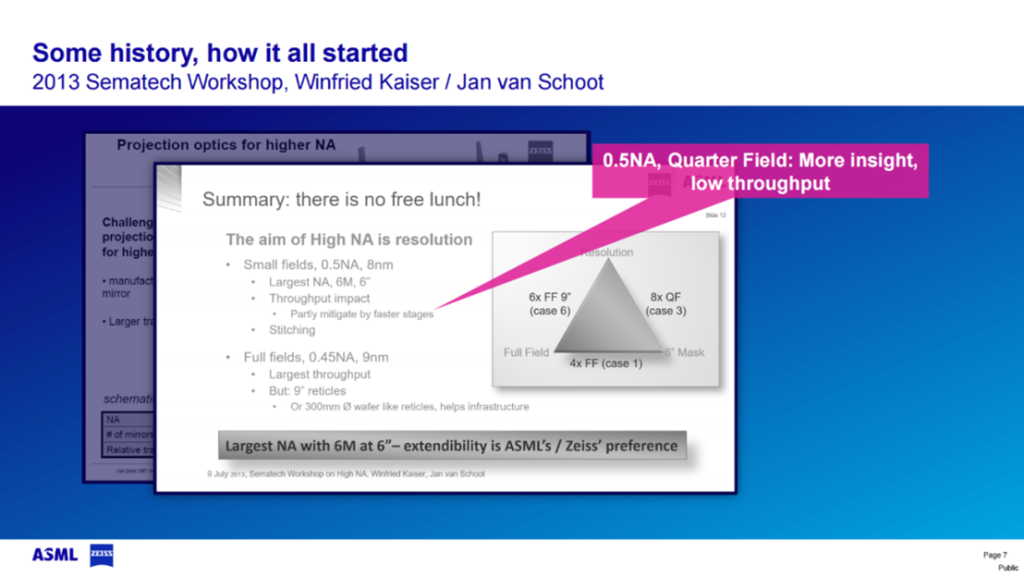

- 高 NA EUV 起点:

- 0.45NA 与 0.5NA 尝试暴露出吞吐量不足等问题;

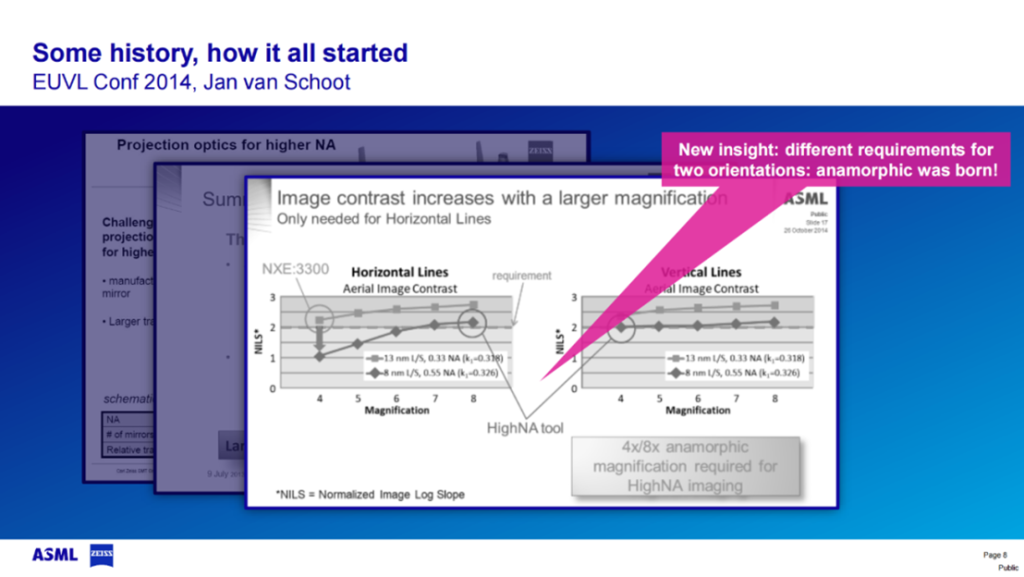

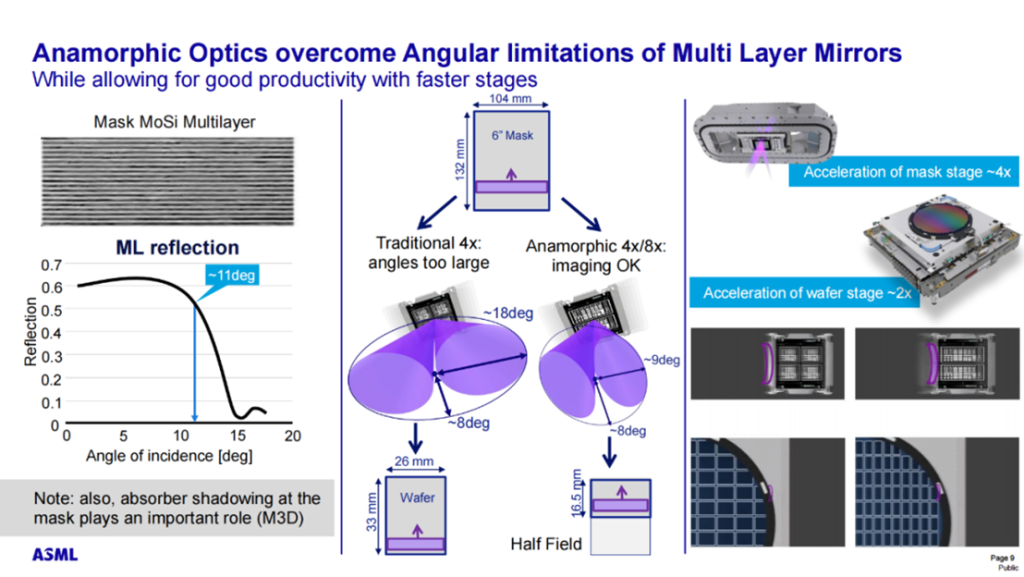

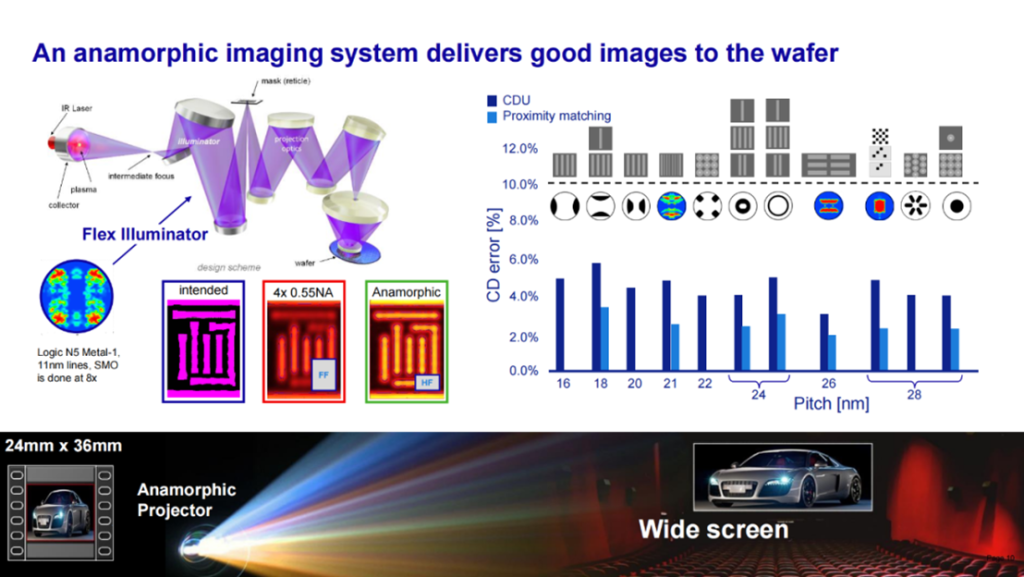

- 2014 年提出非等方成像(anamorphic optics),突破镜面角度限制,同时保证成像和生产效率。

2. 高 NA EUV 工具进展

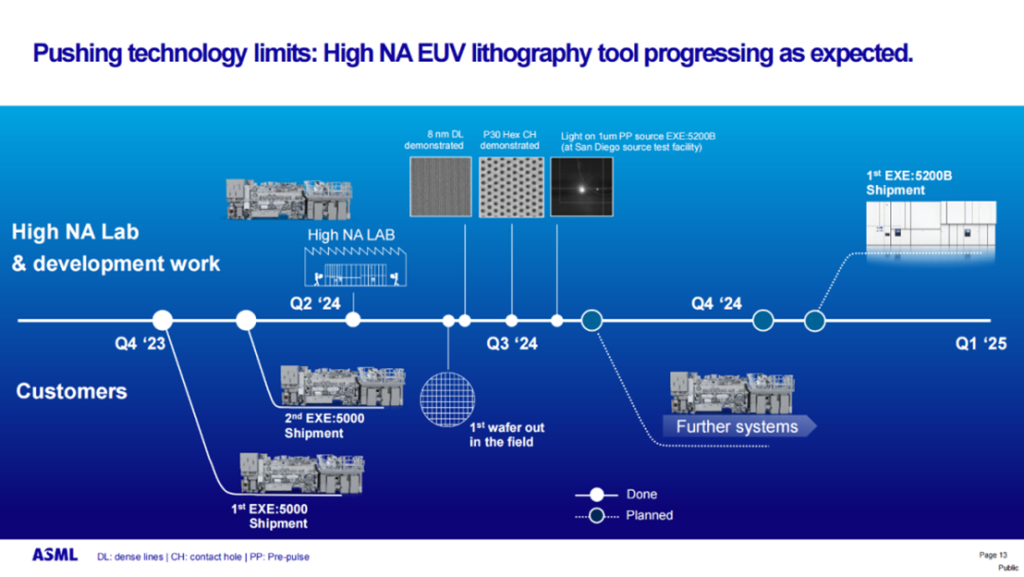

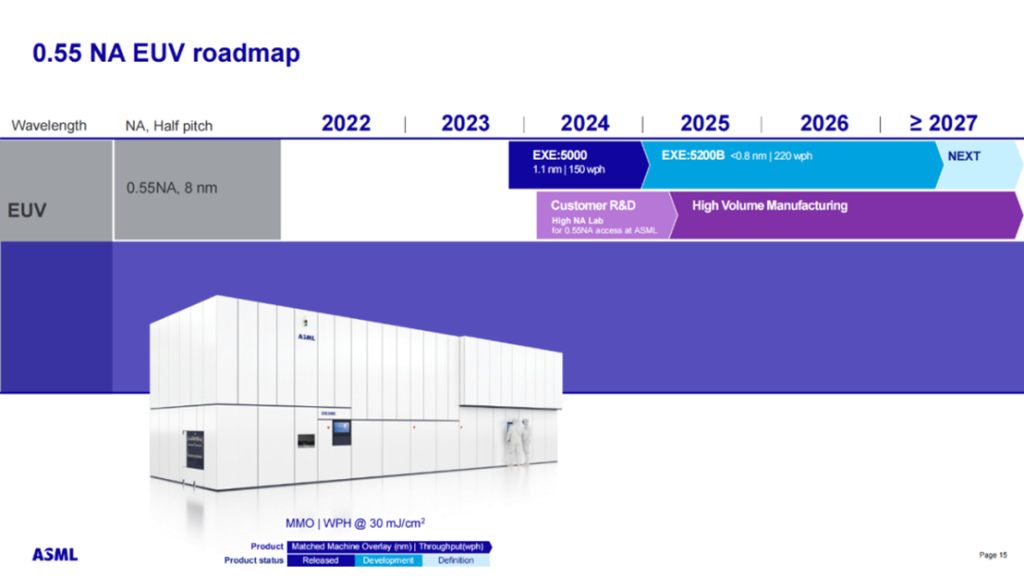

- 时间节点:

- 2023 Q4:首台 EXE:5000 出货。

- 2024:EXE:5000/5200B 多台出货,客户晶圆流片。

- 2025:进入客户研发和量产阶段。

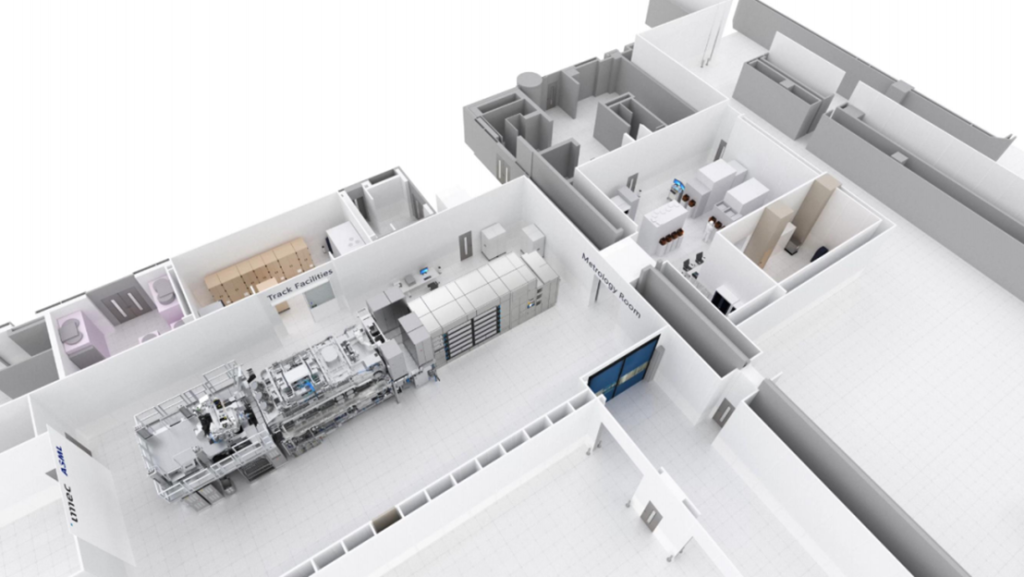

- 高 NA Lab:ASML 已建立完整实验室,支持客户早期工艺开发,计量与工艺验证配套。

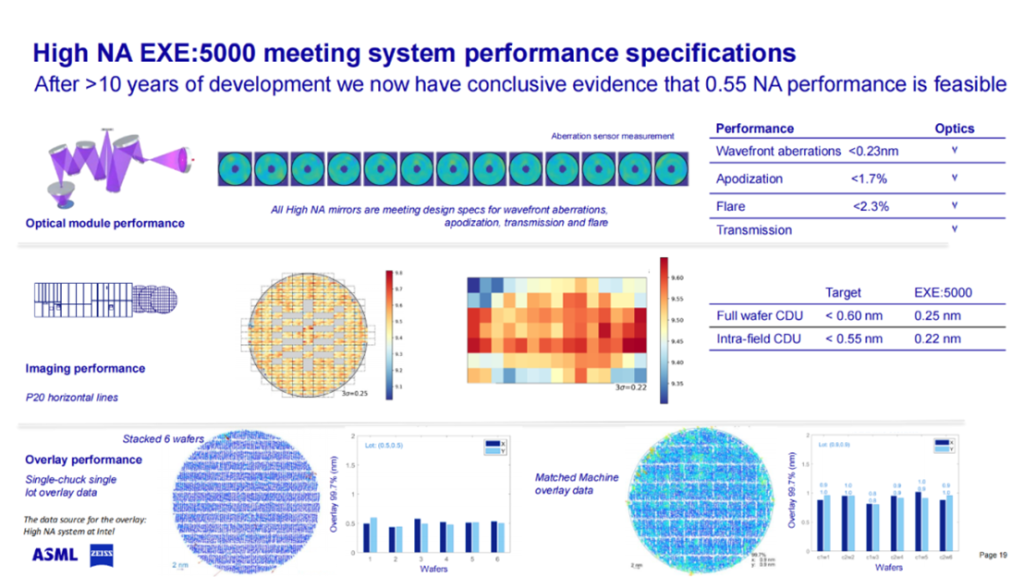

3. 成像与套刻性能

- 光学模块:

- 波前像差 <0.23 nm;

- 衍射光阑畸变(apodization)<1.7%;

- 杂散光(flare)<2.3%;

- 光学传输率达标。

- 系统指标:

- 全场 CDU <0.60 nm;

- 单机 overlay 精度达 99.7%(Intel 数据验证)。

- 结论:经过 10+ 年开发,0.55 NA 的成像与套刻性能已被验证可行。

4. DRAM 应用价值

- 15 nm 接触孔:

- 传统方案:2×0.33 NA + 1×DUV 三重曝光;

- 高 NA:单次曝光即可完成。

- 效益:

- 工艺简化,缺陷率降低;

- 成本下降 ~30%;

- 剂量降低 ~70%;

- 吞吐率提升 ~7 倍。

5. Logic 应用价值

- 随机 Via(30 nm):

- 由双重曝光(0.33 NA)简化为单次曝光(0.55 NA)。

- 成本下降 ~20%,并减少缺陷。

- 金属互连:

- 支持多 pitch、多 CD、多维设计(1.5D/2D interconnect);

- 单次曝光带来 ~35% 成本收益与工艺简化。

6. 技术挑战与突破

- 关键三要素:抗蚀剂、剂量、对比度。

- 高 NA 优势:

- 提升图像对比度,降低局部 CDU 与缺陷。

- 改善“pipe cleaner”效应,减少缺孔。

- 配套需求:高吸收率、低噪声的抗蚀剂,先进掩模和高对比度照明系统。

7. 光源与能效演进

- 功率进展:

- 已实现 740W EUV 输出。

- 目标 >1000W,长期目标 ~2000W(可在满产速率下实现 100 mJ/cm² 剂量)。

- 实现路径:

- 1 µm 激光架构 + 高压液滴发生器(700 bar)已验证 >600W。

- 改进照明结构(减少反射镜数量,提高透过率)。

8. 总结与展望

- 0.55 NA EUV 是 EUV 技术的进化升级,通过提高对比度推动工艺微缩。

- 实验结果:对比 0.33 NA,显著改善 DRAM 与逻辑制程的工艺简化、成本下降与吞吐率提升。

- 经济价值:带来 20–35% 的综合成本节约。

- 生态体系:ASML 高 NA Lab 已开放给客户,支持早期工艺验证。

- 未来方向:EUV 光源功率突破 1000–2000W,确保摩尔定律延续。